Anwendung von SB-ZePoC in einphasigen Umrichtern

| Leitung: | Prof. Dr.-Ing. Axel Mertens |

| Jahr: | 2010 |

| Förderung: | Deutsche Forschungsgemeinschaft (DFG) |

| Laufzeit: | 2 Jahre |

| Ist abgeschlossen: | ja |

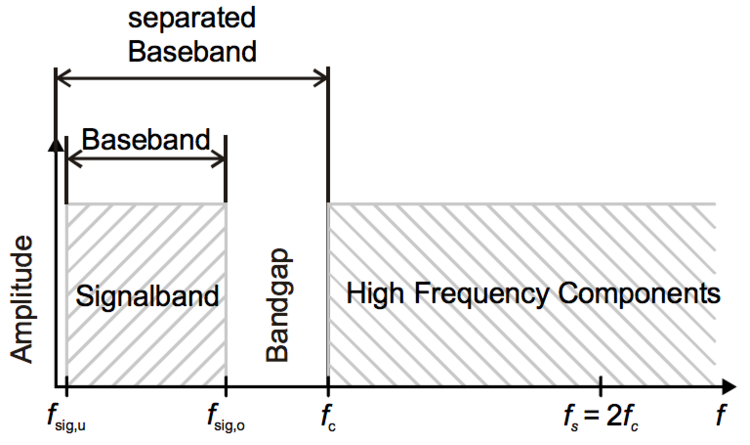

Abb. 1: Bandlücke bei SB-ZePoC (IAL)

Das Verfahren ist unter dem Namen Zero-Position-Coding mit separiertem Basisband (SB-ZePoC) bekannt und wurde für digitale Audioverstärker entwickelt. Auf Basis dieser Überlegungen wird eine Anwendung in der Leistungselektronik zur Pulsmustergenerierung untersucht.

Der SB-ZePoC-Algorithmus besitzt die Eigenschaft einer definierten Bandlücke zwischen dem Bereich der Signalfrequenz (fsig) (hier: gewünschte Grundausgangsfrequenz des Umrichters) und den hochfrequenten Anteilen auf Grund der Schaltfrequenz (fsw) und deren Intermodulationen mit der Signalfrequenz. Diese Bandlücke liegt bei dem Verfahren beim Einsatz einer Halbbrücke zwischen der Signalfrequenz und der halben Schaltfrequenz. Diese Bandlücke wird mit einer Reduktion des maximalen Aussteuergrads bei höheren Signalfrequenzen erkauft.

|  |

Abb. 2: Spannung über der Last bezogen auf die Zwischenkreisspannung bei RPWMDA für fsig 45 Hz, fsw 254 Hz, M 90% | Abb. 3: Spannung über der Last bezogen auf die Zwischenkreisspannung bei SB-ZePoC für fsig 50 Hz, fsw 254 Hz, M 90% |

Im Folgenden werden nun die Vorteile für die Anwendung eines auf dem SB-ZePoC-Verfahren basierenden Steuerverfahrens für einen einphasigen Vollbrücken-Wechselrichter beschrieben. Die Bandlücke reicht hier bis zur vollen Schaltfrequenz. Eine Reduktion des Aussteuergrades muss hier ab einer Taktzahl kleiner als vier erfolgen. Das entwickelte Verfahren wird mit einem zweifach asymmetrisch abgetasteten Pulsweitenmodulationsverfahren (RPWMDA) verglichen. Bei den Ergebnissen sind Effekte aufgrund von notwendigen Totzeiten und Spannungsabfällen über den Halbleiterbauelementen vernachlässigt. Die hieraus resultierenden Effekte treten in gleicher Weise bei beiden Modulationsverfahren in Erscheinung.

|  |

Abb. 4: Spektrum zu RPWMDA aus Abb. 1: fsig 50 Hz, fsw 254 Hz, M 90% | Abb. 5: Spektrum zu SB-ZePoC aus Abb. 2: fsig 50 Hz, fsw 254 Hz, M 90% |

Der Vergleich erfolgt bei einer Signalfrequenz von 45 Hz, einer Schaltfrequenz von 254 Hz (Taktzahl 5,644) und einem Aussteuergrad von 90 %. Aus den zeitlichen Verläufen der auf die Zwischenkreisspannung bezogenen Lastspannung in Abb. 2 und Abb. 3 ergeben sich keine wesentlich erkennbaren Unterschiede. In den Abbildungen ist die Schaltperiode als gestrichelte Linie eingezeichnet. Erst eine spektrale Analyse der Spannung zeigt die wesentlichen Unterschiede in der Spannung. Beim RPWMDA-Verfahren treten erkennbar bei 45 Hz die 3. (135 Hz) und 5. (225 Hz) Harmonische in den Vordergrund (siehe Abb. 4). Diese sind in dem hier vorgestellten Steuerverfahren SB‑ZePoC nicht enthalten (siehe Abb. 5). Dieses weist bis zur Schaltfrequenz (im Spektrum durch eine gestrichelte Linie markiert) keine Störungen auf.

Im weiteren Verlauf der Arbeit wird nun die Realisierung von SB-ZePoC für einen dreiphasigen Umrichter untersucht.