Adaptive Ansteuerverfahren für IGBTs mit digitalisierten Treiberstufen

| Leitung: | Prof. Dr.-Ing. Axel Mertens |

| Jahr: | 2010 |

| Förderung: | Deutsche Forschungsgemeinschaft (DFG) |

| Laufzeit: | 3 Jahre |

| Ist abgeschlossen: | ja |

| Weitere Informationen | <a href="http://gepris.dfg.de/gepris/projekt/114994320" target="_blank">www.gepris.dfg.de</a> |

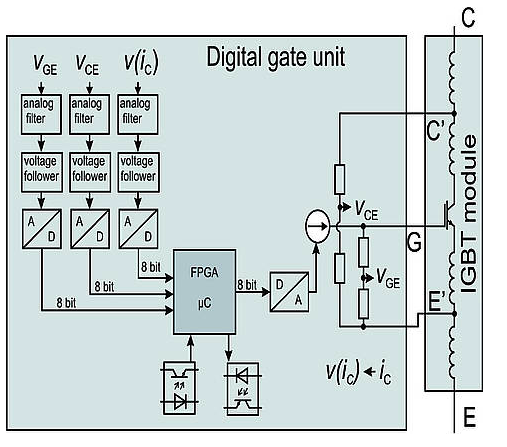

Abb. 1: Prinzipskizze einer digitalisierten Treiberstufe

Im DFG-Projekt „Adaptive Ansteuerverfahren für IGBTs mit digitalisierten Treiberstufen“ werden innovative Methoden untersucht, um das Schaltverhalten von spannungsgesteuerten Halbleiterbauelementen zu optimieren. Stand der Technik ist, dass die Eingangskapazitäten dieser Bauelemente über eine Spannungsquelle und Gate-Vorwiderstände ge- und entladen werden. Die Wahl dieser Vorwiderstände stellt immer einen Kompromiss zwischen verschiedenen Zielen (Verluste, Gradienten) und Randbedingungen (Zwischenkreisspannung, zu schaltender Strom) dar und ist somit in den meisten Fällen kein Optimum.

Ziel in diesem Projekt ist es nun, das Schaltverhalten von leistungselektronischen Hochleistungsbauelementen unabhängig von den Randbedingungen zu optimieren. Dazu muss der Treiber bzw. die darauf implementierte Regelung den Zeitverlauf bestimmter elektrischer Größen und daraus extrahierte Kennwerte wissen. Die Signalverläufe werden dazu digitalisiert und einer Recheneinheit zugeführt. Diese kann nun aus den gewonnenen Informationen in einem implementierten Algorithmus die optimale Stellgröße, den Gatestrom, berechnen. Dieser neue Sollwert wird über eine schnelle analoge Stromquelle dem Gate zugeführt, um den Halbleiterschalter optimal anzusteuern. Eine Prinzipskizze dieser Anordnung ist in Abb. 1 zu sehen.

Ein Prototyp der digitalen Treiberstufe ist in Abb. 2 dargestellt. Man erkennt die Messeinrichtung mit den frequenzkompensierten Spannungsteilern und den drei Analog/Digital-Wandlern für den Kollektorstrom, die Kollektor-Emitter-Spannung und die Gate-Emitter-Spannung. Diese Werte werden dem Entwicklungsboard, eine Kombination von FPGA und Mikrocontroller, zugeführt, auf dem der adaptive Algorithmus implementiert ist. Der darin berechnete, optimierte Gatestrom wird der analogen Strom-Endstufe über einen Digital/Analog-Wandler zugeführt.

Abb. 2: Prototyp einer digitalisierten Treiberstufe

Durch die Tatsache, dass auf der Treibereinheit die Zeitverläufe iC(t), uCE(t) und uGE(t) vorhanden sind, können weitere Informationen über den Halbleiter gesammelt werden: Verluste, Sättigungsspannung, Temperatur, (über temperatursensitive elektrische Parameter) und möglicherweise in Zukunft Veränderungen des thermischen Widerstandes Rth. Das Wissen über die thermische Impedanz und die Sättigungsspannung kann genutzt werden, um auf den Zustand interner Lötungen und den Zustand von Bonddrahtverbindungen zurückzuschließen.

Der Einsatz dieser Treibereinheiten mit den adaptiven Ansteuerverfahren soll es ermöglichen, die Halbleiter über den gesamten Einsatzbereich besser ausnutzen zu können und somit die Leistungsdichte von Hochleistungsumrichtern noch weiter zu erhöhen. Weitere Vorteile werden von der besseren Kenntnis des Betriebszustands erwartet.

Ansprechpartner Leibniz Universität Hannover

| Prof. Dr.-Ing. Axel Mertens | |

| Fakultät für Elektrotechnik und Informatik, Institut für Antriebssysteme und Leistungselektronik (IAL) | |

| mertens@ial.uni-hannover.de |